About DASIP

The Workshop on Design and Architectures for Signal and Image Processing (DASIP) provides an inspiring international forum for the latest innovations and developments in the field of leading signal, image and video processing and machine learning in custom embedded, edge and cloud computing architectures and systems.

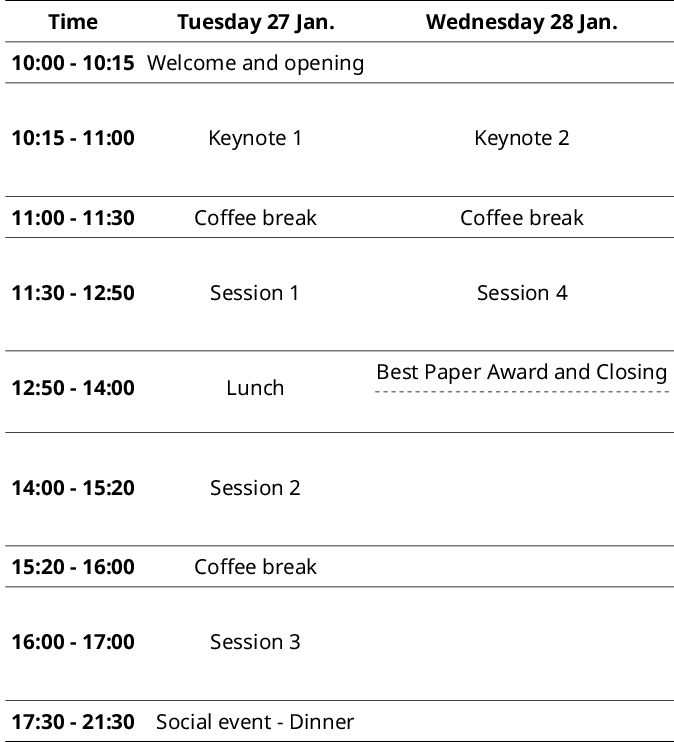

The workshop program will include keynote speeches and contributed paper sessions.

The DASIP 2026 proceedings will be published in the Springer LNCS Series and made available on the Springer website.

Selected papers of DASIP 2026 will be invited to submit an extended version of their work to Elsevier's Journal of Systems Architecture (JSA).

Venue

The 19th Workshop on Design and Architectures for Signal and Image Processing

(DASIP 2026) will take place in conjunction with the

HiPEAC 2026 conference

in Kraków, Poland, 26-28 January 2026.

Important Dates

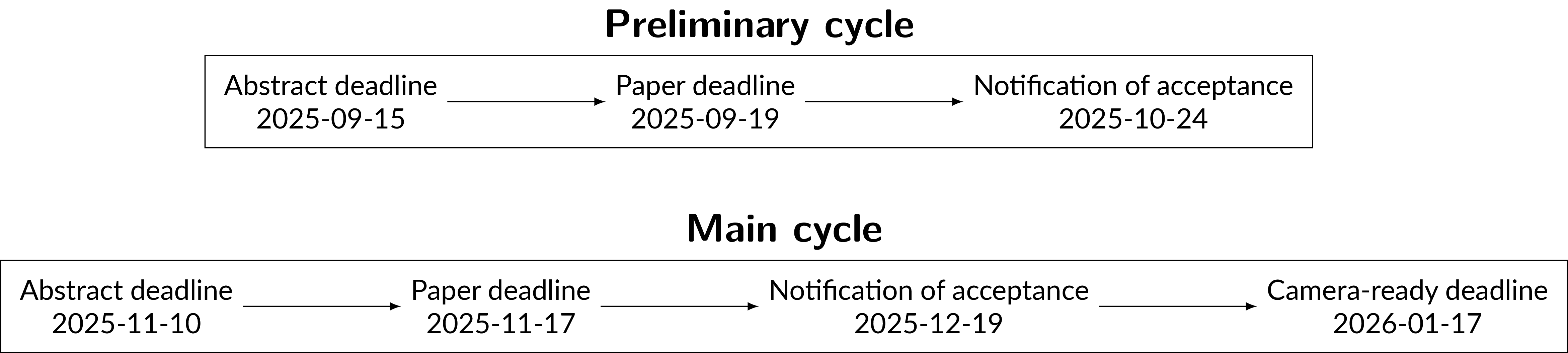

Preliminary Cycle

15 September 2025 → 21 September 2025

Paper submission deadline: 19 September 2025 → 26 September 2025

Notification and feedbacks: sent

Main Cycle

10 November 2025 → 17 November 2025

Paper submission deadline: 17 November 2025 → 24 November 2025

Notification: sent

Camera-ready submission deadline: 17 January 2026

All deadlines are for 23:59 Anywhere on Earth (AoE)